## Am1601 Programmer's Reference Issue 1.0.12 October 29, 2002

This document is subject to modification.

The latest version of this document can be found here:

http://www.amsat.org/amsat/projects/ips/Am1601.html

#### Copyright (c) 2001-2002 AMSAT-DL

Permission is granted to copy, distribute and/or modify this document under the terms of the GNU Free Documentation License, Version 1.1 or any later version published by the Free Software Foundation; with no Invariant Sections, with no Front-Cover Texts, and with no Back-Cover Texts.

A copy of the license is included in Appendix C entitled "GNU Free Documentation License".

This document is maintained by Paul C. L. Willmott, VP9MU.

Reports of errors should be sent to vp9mu@amsat.org

DOCUMENT HISTORY LOG

| Status                                         |                      | 20001121(1         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------------------------------------------------|----------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Status<br>(Baseline/<br>Revision/<br>Canceled) | Document<br>Revision | Effective<br>Date  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Baseline                                       | 1.0.0                | October 9,<br>2001 | Initial Draft by Paul Willmott (PCLW)<br>based upon notes by Lyle Johnson (LJ)<br>March 22, 2001                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Revision                                       | 1.0.1                | August 17,<br>2002 | Information on jumps and branches added<br>by PCLW, based upon email from LJ<br>August 10, 2002.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Revision                                       | 1.0.2                | August 18,<br>2002 | Overflow flag conditions and machine<br>cycle info added to instruction<br>descriptions by LJ. Compares and Stack<br>Group instructions added. Corrections<br>to RSC and PSC references in<br>instruction descriptions, these grow up<br>now. References to T and S replaced by<br>P0 and P1 in all sections. Minor<br>formatting edits. PCLW                                                                                                                                                                                                                                                         |

| Revision                                       | 1.0.3                | August 24,<br>2002 | Corrections and edits, CMP & TST P1<br>added, I & IE flags added by LJ. Minor<br>formatting edits. GNU Free<br>Documentation License stuff added. RCMP<br>removed. Even addresses for 16 bit<br>opcodes. Refresh Register, Error<br>Counter and REFRESH, LSL, LSR, ASR,<br>ROL, ROR, CPL (COM), BIT, CLREF,<br>cLOADB, cSTOREB, cpLOADB, cpSTOREB, DI,<br>EI, PUSHREF, POPREF, RTS, EXECUTE,<br>EMULATE, PREPARE instructions added.<br>Traps and Vectors placeholder added.<br>I/O space details, IN & OUTB<br>instructions added. Changes to cpStore<br>description. icLOAD renamed cpLOAD.<br>PCLW |

| Revision                                       | 1.0.4                | August 25,<br>2002 | Formatting tidy-up, not shown in<br>markup. Consistency changes to<br>instruction descriptions. Additions to<br>BIT description. PCLW                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Revision                                       | 1.0.5                | August 27,<br>2002 | Corrections, cIN and cOUTB changed to<br>cpINB and cpOUTB by LJ. Formating<br>changes. * DRAFT * Remove Before Flight<br>added. PCLW.                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Revision                                       | 1.0.6                | August 31,<br>2002 | Miscellaneous edits. Extra stuff on<br>Interrupt/Reset. EA register added and<br>support. Z flag set added to cc based<br>instructions. sLOAD, sSTORE, uNLOAD,                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|          |        |                       | SNLOAD, CNLOAD added. STOR renamed PTOR<br>to avoid confusion with STORES. RTOS<br>renamed to RTOP. Some examples added.<br>PCLW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------|--------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision | 1.0.7  | September<br>7, 2002  | Corrections by LJ. Formatting tidy-up,<br>not shown in markup. PUSHREF, POPREF<br>opcode values changed. PUSHEA, POPEA<br>added. Some examples added, some<br>example placeholders removed. Minor<br>language edits. Vectors for stack<br>underflow added. PCLW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Revision | 1.0.8  | September<br>8, 2002  | Corrections by LJ. Formatting tidy-up.<br>Page numbering changes. cBSR, POPEA<br>removed. PCLW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Revision | 1.0.9  | September<br>14, 2002 | Misc corrections. EMULATE, PREPARE now<br>conditional on External Flag. EXECUTE<br>now conditional on Zero Flag. sBR added<br>as #4x. sBSR changed to #5x. FLAG now 2<br>byte instruction and moved to #FF.<br>uNLOAD, sNLOAD moved to #70, #71. PCLW<br>Corrections by LJ. More corrections by<br>PCLW. Assembler updated.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Revision | 1.0.10 | September<br>19, 2002 | 1 byte instructions changed to 2 byte<br>instructions. PC odd vector added. EF<br>in cc conditionals changed to not EF.<br>BIT renamed as MASK. CLREF, DI, EI,<br>POPREF, PUSHREF, POPEA, RTS deleted.<br>P0/P1 variants of SBC/SUB/CMP reversed<br>with RSBC/RSUB/RCMP. RCMP added back<br>in. DFX, 2BLIT added. Opcode numbers<br>changed everywhere. Corrections and<br>additions by LJ and PCLW. PUSH & POP<br>renamed PUSHPS & POPPS. PUSHRS & POPRS<br>added. SET & CLEAR added. XB (SWAPB)<br>added. EMULATE, EXECUTE. PREPARE &<br>REFRESH now cc conditional. All 16 bit<br>data structures must start at an even<br>address. All instructions except the<br>explicit byte manipulation instructions<br>expect to find a word at an even<br>address. Position of condition code cc<br>changed in opcodes/operands. cIN, cOUT,<br>cINB, cOUTB, cpIN, cpOUT added.<br>cpINB/cpOUTB opcodes changed. |

| Revision | 1.0.11 | September<br>21, 2002 | opcodes for subtracts switched around.<br>FLAG is now a load rather than a push.<br>Minor edits. LJ/PCLW.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Revision | 1.0.12 | October 29,<br>2002   | Changes to FLAG condition codes, and<br>CBR condition codes LJ. Copyright<br>changed from AMSAT-BDA to AMSAT-DL.<br>Minor edits. Am1601 Assembler and IPS-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

## Am1601 Programmer's Reference Revision 1.0.12 - October 29, 2002

|  | F1G | source | code | added | back | in. | PCLW. |

|--|-----|--------|------|-------|------|-----|-------|

|  |     |        |      |       |      |     |       |

|  |     |        |      |       |      |     |       |

|  |     |        |      |       |      |     |       |

## CHAPTER 1 - Am1601 Overview

"The Am1601 is a stack based CPU implemented in a FPGA. Its reason for existence is to allow AMSAT access to an IPS-friendly radiation tolerant processor and to be in control of the intellectual property associated with it."

Lyle Johnson KK7P March 22, 2001

## Am1601 Emulator

An Am1601 emulator program for Windows NT, and a general user version of IPS to run on the emulator is available. The purpose of the emulator is to aid the design and development of the hardware Am1601, not to run "real-life" programs. IPS running on the emulator is considerably slower than it would be on a real hardware machine. That said the emulator is a very useful tool for debugging purposes.

It is made available to the general public for peer review purposes, and is provided "as is".

The emulator program can be downloaded from here:

http://www.amsat.org/amsat/projects/ips/Am1601.html

Additional IPS software and documentation can be found here:

http://www.amsat.org/amsat/sats/ao40/ips.html

## CHAPTER 2 - Am1601 Architecture

## 2.1 Memory Space

The memory in an Am1601 system is a sequence of up to 65536 bytes. A *word* is any two consecutive bytes in memory. Words are stored in memory with the most significant byte at the higher address. Instructions that manipulate 16-bit values expect to find data in memory at even addresses. Only the explicit byte manipulation instructions are able to access data stored at odd addresses.

### 2.2 Stacks

The Am1601 processor has two internal last-in first-out (LIFO) stacks; the *parameter* and the *return*. The parameter stack is used to store data, whilst the return stack stores return addresses etc. These two internal stacks are 16 bits wide and 16 elements deep. These two internal stacks are implemented as bi-directional shift registers, e.g. a push operation onto the parameter stack will cause P14 to be shifted to P15, P13 to P14 etc. The Am1601 transparently handles stack overflow to external memory if necessary, with the only penalty being execution time.

All arithmetic and logical operations are performed on the contents of the parameter stack, with the results being deposited back onto the parameter stack.

| Parameter Stack |     |  |  |  |  |  |

|-----------------|-----|--|--|--|--|--|

| Top->           | P0  |  |  |  |  |  |

| Second->        | P1  |  |  |  |  |  |

| Third->         | P2  |  |  |  |  |  |

|                 | P3  |  |  |  |  |  |

|                 | P4  |  |  |  |  |  |

|                 | P5  |  |  |  |  |  |

|                 | P6  |  |  |  |  |  |

|                 | P7  |  |  |  |  |  |

|                 | P8  |  |  |  |  |  |

|                 | P9  |  |  |  |  |  |

|                 | P10 |  |  |  |  |  |

|                 | P11 |  |  |  |  |  |

|                 | P12 |  |  |  |  |  |

|                 | P13 |  |  |  |  |  |

|                 | P14 |  |  |  |  |  |

|                 | P15 |  |  |  |  |  |

| Return Stack |     |  |  |  |  |  |

|--------------|-----|--|--|--|--|--|

| Top->        | R0  |  |  |  |  |  |

|              | R1  |  |  |  |  |  |

|              | R2  |  |  |  |  |  |

|              | R3  |  |  |  |  |  |

|              | R4  |  |  |  |  |  |

|              | R5  |  |  |  |  |  |

|              | R6  |  |  |  |  |  |

|              | R7  |  |  |  |  |  |

|              | R8  |  |  |  |  |  |

|              | R9  |  |  |  |  |  |

|              | R10 |  |  |  |  |  |

|              | R11 |  |  |  |  |  |

|              | R12 |  |  |  |  |  |

|              | R13 |  |  |  |  |  |

|              | R14 |  |  |  |  |  |

|              | R15 |  |  |  |  |  |

### 2.3 Registers

In addition to the stack registers the Am1601 provides a *program counter (PC)* and a number of IPS-friendly support registers.

2.3.1 Program Counter (PC). The program counter holds the 16-bit address of the current instruction being fetched from memory. The PC is automatically incremented (by 2 or 4 depending upon the instruction being executed) after its contents have been transferred to the address lines. When a program jump occurs, the new value is automatically placed in the PC, overriding the incrementer. If the PC register is loaded with an odd numbered address, then the instruction being executed is aborted, the PC register is loaded with the address of the PC Odd Vector, and program execution continues at the address now indicated by the PC register.

2.3.2 Flag Register (FLAGS) supplies information to the user regarding the status of the Am1601 at any given time. The bit positions for each flag are shown below:

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 EC EC EC EC EC EC X X EE IE I E O S Z C b5 b4 b3 b2 b1 b0

Where:

| С   | = | Carry Flag       |

|-----|---|------------------|

| Ζ   | = | Zero Flag        |

| S   | = | Sign Flag        |

| 0   | = | Overflow Flag    |

| Е   | = | External Flag    |

| I I | = | Interrupt Flag   |

| IΕ  | = | Interrupt Enable |

EC = EDAC Error Counter

X = Not Used

The bits in the least significant byte of the FLAGS register can be set or cleared in software by the SET and CLEAR instructions. It is not recommended that the EE, E or I flags be set in software.

2.3.2.1 Carry Flag (C). The carry bit is set or reset depending on the operation being performed. For ADD instructions that generate a carry and SUBTRACT instructions that generate a borrow, the Carry Flag will be set. The Carry Flag is reset by an ADD that does not generate a carry and a SUBTRACT that doesn't generate a borrow. This saved carry facilitates software routines for extended precision arithmetic.

2.3.2.2 Zero Flag (Z). The Zero Flag is set or reset if the result generated by the execution of certain instructions is zero. For arithmetic and logical operations, the Z flag will be set to a 1 if the resulting word on the top of the parameter stack is zero. If the word is not zero, the Z flag is reset to 0. Certain conditionally executed instructions which may affect the parameter stack depth also set or clear the Z flag upon execution.

2.3.2.3 Sign Flag (S). The Sign Flag (S) stores the state of the most significant bit of the word on the top of the parameter stack (Bit 15). When the Am1601 performs arithmetic operations on signed numbers, binary two's complement notation is used to represent and process numeric information. A positive number is identified by a 0 in bit 15. A negative number is identified by a 1. The binary equivalent of the magnitude of a positive number is stored in bits 0 to 14 for a total range of 0 to 32767. A negative number is represented by the two's complement of the equivalent positive number. The total range for negative numbers is -1 to -32768.

2.3.2.4 Overflow Flag (O). The Overflow Flag (O) is valid for binary two's complement operations only (signed). The Overflow Flag is set to 1 if an overflow occurred, 0 otherwise. If bit 15 of both operands are set to 1, and bit 15 of the result is 0, then an overflow occurred. Likewise if bit 15 of both operands are set to 0, and bit 15 of the result is 1, then an overflow occurred.

2.3.2.5 External Flag (E). The External Flag is a flip-flop that is set by an external event, sampled at an I/O pin. It is cleared in software by the CLEAR instruction with the appropriate mask.

2.3.2.6 Interrupt Flag (I). The Interrupt Flag is set when a maskable interrupt occurs. It is cleared in software by the CLEAR instruction with the appropriate mask.

2.3.2.7 Interrupt Enable Flag (IE). The Interrupt Enable Flag is used to enable or disable the maskable interrupt. It is manipulated in software by the SET and CLEAR instructions with the appropriate mask. It is automatically cleared (disabled) in hardware when an Interrupt is responded to. It must subsequently be enabled by software.

2.3.2.8 EDAC Error Flag (EE). The EDAC Error Flag is set when the EDAC sub-system corrects a bit in memory. When an error is corrected, the EDAC Error Counter (EC) is incremented, and the EDAC Error Address register (EA) is loaded with the address of

the byte or word in memory corrected. It is cleared in software by the CLEAR instruction with the appropriate mask.

2.3.3 Pseudo Program Counter (PPC). The IPS pseudocode is executed by the inner interpreter. This routine employs a pointer, the so-called pseudo-program counter. This PPC points to the next pseudo-instruction to be executed in turn.

2.3.4 Header Pointer (HP). The IPS inner interpreter fetches the contents of the location that the PPC points to and then increments the PPC by two. This fetched number is called the header pointer (HP) and it points to the header of the routine to be executed.

2.3.5 Parameter Stack Pointer (PSP). The parameter stack pointer holds the address in memory of the top of the parameter stack overflow area. The overflow area is only used if the parameter stack contains more than 16 entries. When a value is pushed onto the overflow area, the Parameter Stack Pointer is post-decremented by 2. When a value is popped from the overflow area, the Parameter Stack Pointer Stack Pointer is pre-incremented by 2. The Parameter Stack Pointer must be initialised to an even address by software.

2.3.6 Parameter Stack Counter (PSC). The parameter stack counter is an up/down counter that is incremented every time a push operation on the parameter stack occurs, and is decremented every time a pop operation on the parameter stack occurs. It allows the user to inspect the number of items on the parameter stack. It is also used to implement the parameter stack hardware overflow/underflow mechanism. This register is initialized to zero after a Reset. In the event of an underflow of the parameter stack (PSC decrements to #FFFF), the processor aborts the instruction currently being executed. Then the contents of the Program Counter are pushed onto the return stack. The PC register is then loaded with the address of the Parameter Stack Underflow Vector (#0008) and points to the next instruction to be executed.

2.3.7 Return Stack Pointer (RSP). The return stack pointer holds the address in memory of the top of the return stack overflow area. The overflow area is only used if the return stack contains more than 16 entries. When a value is pushed onto the overflow area, the Return Stack Pointer is post-decremented by 2. When a value is popped from the overflow area, the Return Stack Pointer is pre-incremented by 2. The Return Stack Pointer Stack Pointer is post-decremented by software.

2.3.8 Return Stack Counter (RSC). The return stack counter is an up/down counter that is incremented every time a push operation on the return stack occurs, and is decremented every time a pop operation on the return stack occurs. It allows the user to inspect the number of items on the return stack. It is also used to implement the return stack hardware overflow/underflow mechanism. This register is initialized to zero after a Reset. In the event of an underflow of the return stack (RSC decrements to #FFFF), the processor aborts the instruction currently being executed. Then the contents of the Program Counter are pushed onto the return stack. The PC register is then loaded with the address of the Return Stack Underflow Vector (#0004) and points to the next instruction to be executed.

2.3.9 Refresh Register (RR). The refresh register contains the address of the next memory location to be refreshed. This is used by the REFRESH instruction to implement the EDAC memory wash. The RR register is initialised to #0000 upon reset.

2.3.10 EDAC Error Address (EA). This register holds the address of the last byte or word in memory to be corrected by the EDAC sub-system. The EA register retains its contents through a reset.

- 2.4 Operand Notation

- 2.4.1 The following notation is used in the instruction descriptions:

- 1). P0 specifies the top register of the parameter stack.

- 2). (P0) specifies the contents of memory at the location addressed by the contents of the P0 register.

- 3). R0 specifies the top register of the return stack.

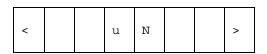

- 4). uN specifies a one byte value in the range 0 to 255.

- 5). sN specifies a one byte signed value in the range –128 to 127.

- 6). abc specifies a12 bit absolute address in the range #0000 to #0FFF. In the operand binary descriptions the "a" represents the high order nibble, and "c" the lowest order nibble.

- efg specifies a 12 bit signed displacement in the range –2048 to 2047, bit

11 (high order bit) contains the sign. In the operand binary descriptions the "e" represents the high order nibble, and "g" the lowest order nibble.

- 8). cc specifies a condition code.

- 9). nnnn specifies a 16 bit value in the range 0 to 65535 (#0000 to #FFFF).

- 10). eeee specifies a 16 bit signed displacement in the range –32768 to 32767.

- 11). ee specifies an 8 bit signed displacement in the range –128 to 127.

- 12). s specifies any of the uN, sN or P1 operands. In the case of the SBC, SUB, and CMP instructions s specifies any of the uN, sN or P0 operands.

- 13). qq specifies any of the PC, PPC, HP, FLAGS, PSP, PSC, RSP, RSC, EA or RR registers.

- 14). Hexadecimal numbers are prefixed in this guide and the assembler by the # character, as per IPS convention.

- 15). <x> specifies a nibble (4 bits), where x can be any character. e.g. for a byte containing #FE, <F> is the high order nibble, and <E> the lower order nibble.

- 16). MSB means the Most Significant Byte of a word. LSB means the least significant byte of a word.

- 17). pppp specifies a 16 bit I/O port address in the range 0 to 65535 (#0000 to #FFFF).

- 18). b0, b1 ... b15 specify an individual bit; b0 specifies bit 0, the lowest significant bit.

- 19). y specifies either of the uN or P0 operands.

- 20). dest <- expr means that the expression expr is loaded into the destination dest. The destination can by a register, memory location, I/O port, or bit in any of the foregoing.

- 21). P0 <<- expr means that the expression expr is pushed onto the top of the parameter stack. Similarly, R0 <<- expr means that the exepression expr is pushed onto the top of the return stack.

- 22). dest <-> dest means that the contents of the two destinations are exchanged, i.e. swapped.

- 23). The enclosing of an expression wholly in parentheses indicates a memory address. The contents of the memory address equivalent to the expression value will be used as the operand value.

- 25). m specifies a bit mask. Within the mask all bits are clear except the one identified by the value of m.

2.5 All instructions and all 16-bit data structures must be stored in a memory location with an even address.

- 2.6 Traps & Vectors

- 2.6.1 The following addresses are set aside for traps and vectors:

#0000 Reset#0004 Return Stack Underflow#0008 Parameter Stack Underflow#000C PC Odd Vector#0010 Maskable Interrupt

2.6.2 An external reset (RST) causes the processor to complete the instruction currently being executed. The RR, PSC and RSC registers are initialised to #0000. All other registers are remain unchanged. Then the Program Counter (PC) is then loaded with the address of the Reset Vector (#0000) and points to the next instruction to be executed.

2.6.3 An external interrupt (INT) causes the maskable interrupt to be disabled. Then the processor completes the instruction currently being executed. Then the contents of the Program Counter are pushed onto the return stack. The PC register is then loaded with the address of the Maskable Interrupt Vector (#0010) and points to the next instruction to be executed.

2.6.4 In the event of an underflow of the return stack (RSC decrements to #FFFF), the processor aborts the instruction currently being executed. Then the contents of the Program Counter are pushed onto the return stack. The PC register is then loaded with the address of the Return Stack Underflow Vector (#0004) and points to the next instruction to be executed.

2.6.5 In the event of an underflow of the parameter stack (PSC decrements to #FFFF), the processor aborts the instruction currently being executed. Then the contents of the Program Counter are pushed onto the return stack. The PC register is then loaded with the address of the Parameter Stack Underflow Vector (#0008) and points to the next instruction to be executed.

2.6.6 In the event of the Program Counter Register (PC) being loaded with an odd value, then the current instruction being executed is aborted. The PC register is loaded with the PC Odd Vector (#000C), and program execution continues at the location indicated by the new contents of the PC register.

2.7 Input / Output (I/O)

2.7.1 The Am1601 has a separate I/O space from memory. This space is a bank of 65536 I/O ports addressed as #0000 to #FFFF. The ports are 8 bits wide. 16 bit ports can be accommodated at even I/O port addresses. The cIN, cOUT, cINB, cOUTB, cpIN, cpOUT, cpINB and cpOUTB instructions are used to read from and write to the I/O ports.

2.8 Undefined Opcodes

2.8.1 The opcode values for which instructions have not been defined, are just that ..."undefined and unpredictable".

## **CHAPTER 3 - Am1601 Instruction Set**

INTRODUCTION:

This chapter describes each Am1601 opcode (instruction) in detail. The opcodes are largely presented in alphabetical order, one per page. Each instruction is introduced by its mnemonic opcode and symbolic operations. Then follows a brief description, operation, valid operand combinations, machine code, detailed description, condition bits affected, and one or more examples.

## 2BLIT

| Operation: | P0 <<- (PPC)   |

|------------|----------------|

|            | PSC <- PSC + 1 |

|            | PPC <- PPC + 2 |

|            | PC <- PC + 2   |

## Format:

2BLIT

#FB

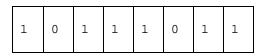

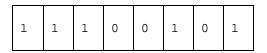

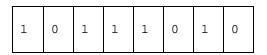

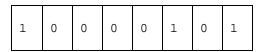

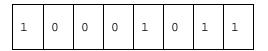

| 1 1 | 1 | 1 | 1 | 1 | 0 | 1 |

|-----|---|---|---|---|---|---|

|-----|---|---|---|---|---|---|

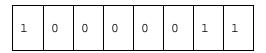

#00

| 0 0 0 | 0 | 0 | 0 | 0 | 0 |

|-------|---|---|---|---|---|

|-------|---|---|---|---|---|

Description:

This instruction fetches a 16-bit word at the address indicated by the Pseudo Program Counter Register (PPC) and pushes it onto the top of the parameter stack (P0). The PPC register is incremented by 2, and program execution continues at the next instruction in memory (PC + 2).

M CYCLES: 4

Condition Bits Affected:

None

# ADC

| Operation: | if operand is uN or sN |

|------------|------------------------|

|            | P0 <- P0 + s + C       |

|            | PC <- PC + 2           |

## Format:

[uN|sN] s ADC

The s operand is any of uN, sN or P1. These various possible opcode-operand combinations are assembled as follows in the object code:

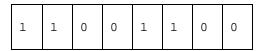

uN uN ADC

#A1

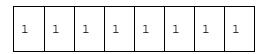

| 1 | 0 | 1 | 0 | 0 | 0 | 0 | 1 |

|---|---|---|---|---|---|---|---|

|---|---|---|---|---|---|---|---|

8-bit unsigned value, this is extended by the processor prior to the operation by filling bits 8 - 15 with zeroes.

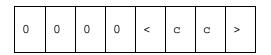

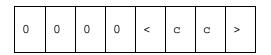

| < | u | N |  |  | > |  |

|---|---|---|--|--|---|--|

|---|---|---|--|--|---|--|

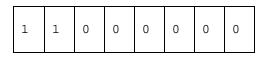

sN sN ADC

#B1

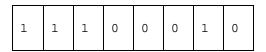

| 1 | 0 | 1 | 1 | 0 | 0 | 0 | 1 |  |

|---|---|---|---|---|---|---|---|--|

|---|---|---|---|---|---|---|---|--|

8-bit signed value, this is extended by the processor prior to the operation by filling bits 8 -15 with the most significant bit of the operand.

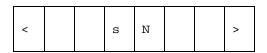

| < |  | S | N |  |  | > |  |

|---|--|---|---|--|--|---|--|

|---|--|---|---|--|--|---|--|

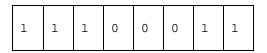

P1 ADC

#C0

#10

| 0 0 0 1 0 0 0 0 |

|-----------------|

|-----------------|

#### Description:

The byte or word specified by the s operand, along with the Carry Flag ("C" in the Flags register) are added to the contents of the top register of the parameter stack (P0); the result replaces the contents of P0. In the case of the P1 variant, the top two entries on the parameter stack are popped and the result pushed onto the top of the parameter stack.

M CYCLES: 2

#### Condition Bits Affected:

- C: Set if carry from Bit 15; reset otherwise

- S: Set if result is negative; reset otherwise

- Z: Set if result is zero; reset otherwise

- O: Set if the signed result is an overflow; reset otherwise

#### Example:

If the P0 register contains #0016, the Carry Flag is set, the P1 register contains #0010, after the execution of

#### P1 ADC

the P0 register will contain #0027.

# ADD

| Operation: | if operand is uN or sN |

|------------|------------------------|

|            | P0 <- P0 + s           |

|            | PC <- PC + 2           |

|            | if aparand D1          |

### Format:

[uN|sN] s ADD

The s operand is any of uN, sN or P1. These various possible opcode-operand combinations are assembled as follows in the object code:

uN uN ADD

#A0

| 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 |

|---|---|---|---|---|---|---|---|

|---|---|---|---|---|---|---|---|

8-bit unsigned value, this is extended by the processor prior to the operation by filling bits 8 - 15 with zeroes.

| < | u | N |  |  | > |  |

|---|---|---|--|--|---|--|

|---|---|---|--|--|---|--|

sN sN ADD

#B0

| 1 | 0 | 1 | 1 | 0 | 0 | 0 | 0 |  |

|---|---|---|---|---|---|---|---|--|

|---|---|---|---|---|---|---|---|--|

8-bit signed value, this is extended by the processor prior to the operation by filling bits 8 - 15 with the most significant bit of the operand.

| < |  | S | N |  |  | > |

|---|--|---|---|--|--|---|

|---|--|---|---|--|--|---|

P1 ADD

#C0

| 1 1 0 | 0 | 0 | 0 | 0 | 0 |  |

|-------|---|---|---|---|---|--|

|-------|---|---|---|---|---|--|

#00

| 0 0 0 0 0 0 0 0 |

|-----------------|

|-----------------|

#### Description:

The byte or word specified by the s operand is added to the contents of the top register of the parameter stack (P0); the result replaces the contents of P0. In the case of the P1 variant, the top two entries on the parameter stack are popped and the result pushed onto the top of the parameter stack.

#### M CYCLES: 2

#### Condition Bits Affected:

- C: Set if carry from Bit 15; reset otherwise

- S: Set if result is negative; reset otherwise

- Z: Set if result is zero; reset otherwise

- O: Set if the signed result is an overflow; reset otherwise

#### Example:

If the contents of the P0 register are #00A0, and the uN operand has the value #02, after the execution of

#### #02 uN ADD

the P0 register will contain #00A2.

## AND

| Operation: | if operand is uN or sN |

|------------|------------------------|

|            | P0 <- P0 AND s         |

|            | PC <- PC + 2           |

if operand is P1 P0 <- P0 AND P1 PSC <- PSC - 1 PC <- PC + 2

## Format:

[uN|sN] s AND

The s operand is any of uN, sN or P1. These various possible opcode-operand combinations are assembled as follows in the object code:

uN uN AND

#A6

| 1 | 0 | 1 | 0 | 0 | 1 | 1 | 0 |

|---|---|---|---|---|---|---|---|

|---|---|---|---|---|---|---|---|

8-bit unsigned value, this is extended by the processor prior to the operation by filling bits 8 - 15 with zeroes.

| < | u | N |  |  | > |  |

|---|---|---|--|--|---|--|

|---|---|---|--|--|---|--|

sN sN AND

#B6

| 1 | 0 | 1 | 1 | 0 | 1 | 1 | 0 |  |

|---|---|---|---|---|---|---|---|--|

|---|---|---|---|---|---|---|---|--|

8-bit signed value, this is extended by the processor prior to the operation by filling bits 8 - 15 with the most significant bit of the operand.

| < | S | N |  |  | > |  |

|---|---|---|--|--|---|--|

|---|---|---|--|--|---|--|

P1 AND

#C0

| 1 1 0 0 0 0 0 0 |

|-----------------|

|-----------------|

#60

| 0 1 1 0 0 0 0 0 |

|-----------------|

|-----------------|

#### Description:

A logical AND operation, bit by bit, is performed between the byte or word specified by the s operand and the contents of the top register of the parameter stack (P0); the result replaces the contents of P0. In the case of the P1 variant, the top two entries on the parameter stack are popped and the result pushed onto the top of the parameter stack.

#### M CYCLES: 2

#### Condition Bits Affected:

- C: Reset

- S: Set if result is negative; reset otherwise

- Z: Set if result is zero; reset otherwise

- O: Reset.

#### Example:

If the P0 register contains #007B (B000000001111011) and the P1 register contains #00C3 (B000000011000011) after the execution of

#### P1 AND

the P0 register will contain #0043 (B0000000001000011).

## ASR

<u>Operation:</u> P0 <- P0, C<b0, b0<b1, b1<-b2 .. b14<b15, b15<b15 PC <- PC + 2

Format:

ASR

#C2

| 1 | 1 | 0 | 0 | 0 | 0 | 1 | 0 |  |

|---|---|---|---|---|---|---|---|--|

|---|---|---|---|---|---|---|---|--|

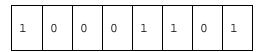

#90

| 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 |  |

|---|---|---|---|---|---|---|---|--|

|---|---|---|---|---|---|---|---|--|

## Description:

An arithmetic shift right is performed on the contents of the top register of the parameter stack (P0). The content of bit 15 (b15) is copied into bit 14 (b14); the previous content of bit 14 is copied into bit 13; this pattern is continued throughout the word. The content of bit 0 (b0) is copied into the Carry Flag ("C" in the FLAGS register), and the previous content of bit 15 (b15) is unchanged. Bit 0 (b0) s the least significant bit.

## M CYCLES: 2

## Condition Bits Affected:

- C: Data from Bit 0 of previous contents of P0

- S: Set if result is negative; reset otherwise

- Z: Set if result is zero; reset otherwise

- O: Reset.

#### Example:

If the P0 register contains #8038 (B100000000111000) after the execution of

ASR

the contents of the P0 register will be #C01C (B110000000011100) and the Carry Flag will contain 0.

## cBR

```

<u>Operation:</u> if condition cc = 0

PC <- PC + 2

```

## Format:

The cc operand is any of the condition codes as defined for the FLAG instruction. ee is the destination displacement.

ee cc cBR

#9<cc>

| 1 | 0 | 0 | 1 | < | С | С | > |

|---|---|---|---|---|---|---|---|

| 1 | 0 | 0 | - | / | ر | ر | 1 |

ee

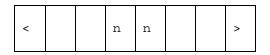

| < |  |  | е | е |  |  | > |  |

|---|--|--|---|---|--|--|---|--|

|---|--|--|---|---|--|--|---|--|

## Description:

This instruction provides for conditional branching. If the condition cc is met then the destination displacement (ee) is added to the Program Counter (PC) + 2 and the next instruction is fetched from the location designated by the new contents of the PC. This jump is measured from the address of the instruction opcode + 2 and has a range of -128 to 127. If the condition is not met then the address of the next instruction in memory (PC + 2) is loaded into the PC register and points to the next program instruction to be executed.

The assembler provides the following definitions to aid the computation of jump offsets:

cc cBRbeginStores opcode and leaves address of the place to insert the jump<br/>offset on top of the IPS-X parameter stack.cBRelseCalculates and inserts the required jump offset into the address<br/>previously deposited by cBRbegin on the top of the IPS-X<br/>parameter stack. The address is popped and discarded. Then an<br/>AL cBR is assembled into the code, and the address of the place<br/>to insert the jump offset is pushed onto the top of the IPS-X<br/>parameter stack.

cBRend Calculates and inserts the required jump offset into the address previously deposited by cBRbegin or cBRelse. The address is popped and discarded.

M CYCLES: 3 if branch taken; 2 if branch not taken.

Condition Bits Affected:

None

#### Example:

To jump forward 6 locations from address #0480 if the Z flag is set, the following assembly language statement is used:

#### 4 EQ cBR

The resulting object code and final PC value is shown below:

| Location                 | <u>Contents</u>  |

|--------------------------|------------------|

| 480<br>481<br>482<br>483 | #90<br>#04       |

| 484<br>485               |                  |

| 486                      | <- PC after jump |

\* DRAFT \*

## sBR

Operation: PC <- PC + efg + 2

Format:

efg sBR

#4<e>

| 0 1 | o o | < | е |  | > |  |

|-----|-----|---|---|--|---|--|

|-----|-----|---|---|--|---|--|

<f><g>

| < | f |  | > | < | g |  | > |  |

|---|---|--|---|---|---|--|---|--|

|---|---|--|---|---|---|--|---|--|

#### Description:

This instruction provides for unconditional branching. The value of the displacement efg is added to the contents of the Program Counter (PC) + 2 and the next instruction is fetched from the location designated by the new contents of the PC. This jump is measured from the address of the instruction opcode + 2 and has a range of -2048 to 2047.

The assembler provides the following definitions to aid the computation of jump offsets:

- sBRbegin Stores opcode and leaves address of the place to insert the jump offset on top of the IPS-X parameter stack.

- sBRcomplete Calculates and inserts the required jump offset into the address previously deposited by sBRbegin. The address is popped and discarded.

M CYCLES: 3

Condition Bits Affected:

None

Example:

To jump to the address #0108, the following assembly language statement is used:

#006 sBR

The resulting object code and final PC value is shown below:

| Location | Contents         |

|----------|------------------|

| 100      | #40              |

| 101      | #06              |

| 102      |                  |

| 103      |                  |

| 104      |                  |

| 105      |                  |

| 106      |                  |

| 107      |                  |

| 108      | <- PC after jump |

# cpBSR

| Operation: | if condition cc = 0<br>PSC <- PSC - 1<br>PC <- PC + 2                                        |

|------------|----------------------------------------------------------------------------------------------|

|            | if condition cc = 1<br>R0 <- PC + 2<br>RSC <- RSC + 1<br>PC <- PC + P0 + 4<br>PSC <- PSC - 1 |

## Format:

cc cpBSR

The cc operand is any of the condition codes as defined for the FLAG instruction.

cc cpBSR

#8F

| 1 | 0 | 0 | 0 | 1 | 1 | 1 | 1 |

|---|---|---|---|---|---|---|---|

|   |   |   |   |   |   |   |   |

#0<cc>

| 0 | 0 | 0 | 0 | < | С | С | ^ |

|---|---|---|---|---|---|---|---|

|---|---|---|---|---|---|---|---|

## Description:

This instruction provides for conditional branching to a subroutine. If the condition cc is met then the address of the next instruction in memory (PC + 2) is pushed onto the return stack. The displacement value is popped off the parameter stack and added to the contents of the Program Counter (PC) + 4 and the next instruction is fetched from the location designated by the new contents of the PC. This jump is measured from the address of the instruction opcode + 4 and has a range of -32768 to 32767. If the condition is not met then the top of the parameter stack is popped and the address of the next instruction in memory (PC + 2) is loaded into the PC register and points to the next program instruction to be executed.

M CYCLES: 3 if branch taken; 2 if branch not taken.

## Condition Bits Affected:

None

## Example:

If the top register of the parameter stack (P0) contains 4. To jump to a subroutine located at the displacement indicated by the P0 register if the Z flag is set, the following assembly language statement is used:

## EQ cpBSR

The resulting object code and final PC value is shown below:

| Location                                      | Contents                                      |

|-----------------------------------------------|-----------------------------------------------|

| 480<br>481<br>482<br>483<br>484<br>485<br>486 | #8F<br>#00<br><- PC after jump, R0 <<- PC + 2 |

|                                               |                                               |

## sBSR

| Operation: | R0 <- PC + 2       |

|------------|--------------------|

|            | RSC <- RSC + 1     |

|            | PC <- PC + efg + 2 |

Format:

efg sBSR

#5<e>

| 0 1 0 1 < | e > |

|-----------|-----|

|-----------|-----|

<f><g>

| < f | > < | а | > |

|-----|-----|---|---|

|-----|-----|---|---|

Description:

This instruction provides for unconditional branching to a subroutine. The address of the next instruction to be executed is pushed onto the return stack. Then the value of the displacement efg is added to the contents of the Program Counter (PC) + 2 and the next instruction is fetched from the location designated by the new contents of the PC. This jump is measured from the address of the instruction opcode + 2 and has a range of -2048 to 2047.

- cc sBSRbegin Stores opcode and leaves address of the place to insert the jump offset on top of the IPS-X parameter stack.

- sBSRcomplete Calculates and inserts the required jump offset into the address previously deposited by sBSRbegin. The address is popped and discarded.

M CYCLES: 3

Condition Bits Affected:

None

Example:

To jump to a subroutine located at address #0108, the following assembly language statement is used:

### #008 sBSR

The resulting object code and final PC value is shown below:

2

| Contents                      |

|-------------------------------|

| #50                           |

| #06                           |

|                               |

|                               |

|                               |

|                               |

|                               |

|                               |

| <- PC after jump, R0 <<- PC + |

|                               |

## CLEAR

Operation: FLAGS <<- FLAGS AND NOT MASK(m) PC <- PC + 2

Format:

m CLEAR

#D5

| 1 1 | 1 0 | 1 | 0 | 1 | 0 | 1 |  |

|-----|-----|---|---|---|---|---|--|

|-----|-----|---|---|---|---|---|--|

#<m>0

| < m > 0 0 0 0 |

|---------------|

|---------------|

### Description:

The bit corresponding to the value of m in the FLAGS register is cleared according to the following table:

| FLAGS bit                  | <u>m</u>                                     |                                        |

|----------------------------|----------------------------------------------|----------------------------------------|

| C<br>Z<br>S<br>O<br>E<br>I | 0000<br>0001<br>0010<br>0011<br>0100<br>0101 | #00<br>#01<br>#02<br>#03<br>#04<br>#05 |

| IE                         | 0110                                         | #06                                    |

| EE                         | 0111                                         | #07                                    |

|                            |                                              |                                        |

## M CYCLES: 2

### Condition Bits Affected:

The bit indicated by the m operand is cleared.

## CMP

```

<u>Operation:</u>

if operand is uN or sN

P0 - s

PC <- PC + 2

if operand is P0

P1 - P0

PC <- PC + 2

```

### Format:

[uN|sN] s CMP

The s operand is any of uN , sN or P0. These various possible opcode-operand combinations are assembled as follows in the object code:

uN uN CMP

#AB

| 1 | 0 | 1 | 0 | 1 | 0 | 1 | 1 |

|---|---|---|---|---|---|---|---|

|---|---|---|---|---|---|---|---|

8-bit unsigned value, this is extended by the processor prior to the operation by filling bits 8 - 15 with zeroes.

| < | u | N |  |  | > |

|---|---|---|--|--|---|

|---|---|---|--|--|---|

sN sN CMP

#BB

8-bit signed value, this is extended by the processor prior to the operation by filling bits 8 - 15 with the most significant bit of the operand.

| < | S | N |  |  | > |  |

|---|---|---|--|--|---|--|

|---|---|---|--|--|---|--|

P0 CMP

#C0

| 1 1 0 0 0 0 0 0 |

|-----------------|

|-----------------|

#A0

| 1 0 | 1 | 0 | 0 | 0 | 0 | 0 |

|-----|---|---|---|---|---|---|

|-----|---|---|---|---|---|---|

#### Description:

In the case of the sN or uN variants the word specified by the s operand is compared to (subtracted from) the contents of the top register of the parameter stack (P0) and the condition flags are set. In the case of the P0 variant the top register of the parameter stack (P0) is compared to (subtracted from) the second register of the parameter stack (P1) and the condition flags are set. The contents of the parameter stack remain unchanged.

#### M CYCLES: 2

#### Condition Bits Affected:

- C: Set if there was a borrow; reset otherwise

- S: Set if result is negative; reset otherwise

- Z: Set if result is zero; reset otherwise

- 0: Set if signed overflow; reset otherwise

#### Example:

If the P0 register contains #FF45 and the P1 register contains #FF45, then after the execution of

#### P0 CMP

the Zero Flag (Z) will be set

\* DRAFT \*

## CPL

| Operation: | P0 <- 1 - P0 |

|------------|--------------|

|            | PC <- PC + 2 |

Format:

CPL

#C0

| 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 |  |

|---|---|---|---|---|---|---|---|--|

|---|---|---|---|---|---|---|---|--|

#D0

|  | 1 | 1 | 0 | 1 | 0 | 0 | 0 | 0 |

|--|---|---|---|---|---|---|---|---|

|--|---|---|---|---|---|---|---|---|

## Description:

The contents of the top register of the parameter stack (P0) are inverted (1's complement). This is the same as subtracting the contents of the P0 register from 1.

## M CYCLES: 2

## Condition Bits Affected:

- C: Set if P0 was not #0001 before operation; reset otherwise.

- S: Set if result is negative; reset otherwise.

- Z: Set if result is 0; reset otherwise.

- O: Reset.

## Example:

If the contents of the P0 register are #00B4 (B000000010110100), after the execution of

## CPL

the P0 register will be #FF4B (B111111101001011).

\* DRAFT \*

## DEL

Operation: PSC <- PSC - 1 PC <- PC + 2

Format:

DEL

#C1

| 1 | 1 | 0 | 0 | 0 | 0 | 0 | 1 |  |

|---|---|---|---|---|---|---|---|--|

|---|---|---|---|---|---|---|---|--|

#10

| 0 | ~ | ~ | - | ~ | ~ | ~ | ~ |

|---|---|---|---|---|---|---|---|

| 0 | 0 | 0 | T | 0 | 0 | 0 | 0 |

|   |   |   |   |   |   |   |   |

|   |   |   |   |   |   |   |   |

## Description:

The top entry of the parameter stack is popped and discarded.

M CYCLES: 2

Condition Bits Affected:

None

## Example:

|                   | P2 | P1 | P0 |

|-------------------|----|----|----|

| Before operation: | 8  | 5  | 12 |

| After operation:  | -  | 8  | 5  |

## DFX

| Operation: | R0 <<- PPC     |  |  |

|------------|----------------|--|--|

|            | RSC <- RSC + 1 |  |  |

|            | PPC <- HP      |  |  |

|            | PC <- PC + 2   |  |  |

## Format:

DFX

#F8

| 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 |

|---|---|---|---|---|---|---|---|

|---|---|---|---|---|---|---|---|

#00

| 0 0 0 0 | 0 0 | 0 | 0 |

|---------|-----|---|---|

|---------|-----|---|---|

Description:

Definition Executive: the contents of the Pseudo Program Counter Register (PPC) are pushed onto the top of the return stack (R0), then the contents of the PPC register are replaced by the contents of the Header Pointer Register (HP). Program execution continues at the next instruction in memory (PC + 2).

M CYCLES: 3

Condition Bits Affected:

None

### DUPL

| Operation: | P0 <<- P0      |

|------------|----------------|

|            | PSC <- PSC + 1 |

|            | PC <- PC + 2   |

### Format:

DUPL

#C1

| 1 1 0 0 | 0 0 | 0 1 |

|---------|-----|-----|

|---------|-----|-----|

#00

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

|---|---|---|---|---|---|---|---|

|---|---|---|---|---|---|---|---|

#### **Description:**

The contents of the top register of the parameter stack (P0) are pushed onto the top of the stack, i.e. duplicated.

### M CYCLES: 2

Condition Bits Affected:

None

Example:

|                   | P2 | P1 | P0 |

|-------------------|----|----|----|

| Before operation: |    | 5  | 12 |

| After operation:  | 5  | 12 | 12 |

# EOR

| <b>Operation:</b> | if operand is uN or sN |

|-------------------|------------------------|

|                   | P0 <- P0 EOR s         |

|                   | PC <- PC + 2           |

### Format:

[uN|sN] s EOR

The s operand is any of uN, sN or P1. These various possible opcode-operand combinations are assembled as follows in the object code:

uN uN EOR

#A8

| 1 | 0 | 1 | 0 | 1 | 0 | 0 | 0 |

|---|---|---|---|---|---|---|---|

|---|---|---|---|---|---|---|---|

8-bit unsigned value, this is extended by the processor prior to the operation by filling bits 8 - 15 with zeroes.

| < | u | N |  |  | > |  |

|---|---|---|--|--|---|--|

|---|---|---|--|--|---|--|

sN sN EOR

#B8

| 1 | 0 | 1 | 1 | 1 | 0 | 0 | 0 |

|---|---|---|---|---|---|---|---|

|---|---|---|---|---|---|---|---|

8-bit signed value, this is extended by the processor prior to the operation by filling bits 8 - 15 with the most significant bit of the operand.

| < |  |  | ß | N |  |  | > |

|---|--|--|---|---|--|--|---|

|---|--|--|---|---|--|--|---|

P1 EOR

#C0

| 1 1 0 0 0 0 0 0 |

|-----------------|

|-----------------|

#80

| 1 0 0 0 0 0 0 0 |

|-----------------|

|-----------------|

#### Description:

A logical exclusive-OR operation, bit by bit, is performed between the byte or word specified by the s operand and the contents of the top register of the parameter stack (P0); the result replaces the contents of P0. In the case of the P1 variant, the top two entries on the parameter stack are popped and the result pushed onto the top of the parameter stack.

M CYCLES: 2

#### Condition Bits Affected:

- C: Reset

- S: Set if result is negative; reset otherwise

- Z: Set if result is zero; reset otherwise

- O: Reset

#### Example:

If the P0 register contains #0096 (B000000010010110), and the operand uN has the value #5D (B01011101), then after the execution of

#### #0096 uN EOR

the P0 register will contain #00CB (B000000011001011).

### **EMULATE** (not available in prototype)

Operation:

```

if condition cc = 1

HP <- (PPC)

PPC <- PPC + 2

PC <- (HP)

HP <- HP + 2

if condition cc = 0

PC <- PC + 2

```

### Format:

### cc EMULATE

The cc operand is any of the condition codes as defined for the FLAG instruction.

### cc EMULATE

#F0

| 1 1 1 1 | L O | 0 | 0 | 0 |  |

|---------|-----|---|---|---|--|

|---------|-----|---|---|---|--|

#0<cc>

| 0 | 0 | 0 | 0 | < | С | С | > |

|---|---|---|---|---|---|---|---|

|---|---|---|---|---|---|---|---|

### Description:

If the condition cc is met, then EMULATE loads the Header Pointer Register (HP) with the contents of the word in memory at the address indicated by the Pseudo Program Counter Register (PPC). The PPC register is incremented by 2. The Program Counter (PC) is then loaded with the address stored at the location indicated by the new contents of the HP register. The HP register is then incremented by 2. Program execution continues from the location now stored in the PC register. If the condition cc is not met then program execution continues at the next instruction (PC + 2).

M CYCLES: 5 cycles if cc, 2 cycles if not cc

### Condition Bits Affected:

### EXECUTE

Format:

cc EXECUTE

The cc operand is any of the condition codes as defined for the FLAG instruction.

cc EXECUTE

#F1

| 1 | 1 | 1 | 1 | 0 | 0 | 0 | 1 |

|---|---|---|---|---|---|---|---|

|---|---|---|---|---|---|---|---|

#0<cc>

| 0 | 0 | 0 | 0 | < | С | С | > |

|---|---|---|---|---|---|---|---|

|---|---|---|---|---|---|---|---|

#### Description:

If the condition cc is met then the Program Counter (PC) is loaded with the address stored at the location indicated by the contents of the Header Pointer Register (HP). The HP register is then incremented by 2. Program execution continues from the location now stored in the PC register. If the condition cc is not met then program execution continues at the next instruction in memory (PC + 2).

MCYCLES: 3 cycles if cc; 2 cycles if not cc

Condition Bits Affected:

## FLAG

| Operation: | if condition $cc = 0$ |

|------------|-----------------------|

|            | P0 <<- #0000          |

|            | PC <- PC + 2          |

if condition cc = 1 P0 <<-#0001 PC <- PC + 2

Format:

cc FLAG

#FF

#0<cc>

| 0 | 0 | 0 | 0 | < | С | С | > |

|---|---|---|---|---|---|---|---|

|---|---|---|---|---|---|---|---|

**Description:**

If the condition cc is met, then #0001 replaces the contents of the top register of the parameter stack (P0). If the condition is not met then #0000 replaces the contents of the P0 register.

### Condition Codes

| #0 | EQ    | Equal, Zero Flag (Z) = 1                      |

|----|-------|-----------------------------------------------|

| #1 | NE    | Not Equal, Zero Flag (Z) = $0$                |

| #2 | CS/HI | Carry Set/Higher, Carry Flag (C) = 1          |

| #3 | CC/LS | Carry Clear/Lower or Same, Carry Flag (C) = 0 |

| #4 | MI    | Minus, Sign Flag (S) = 1                      |

| #5 | PL    | Plus, Sign Flag (S) = $0$                     |

| #6 | VS    | Overflow Flag (O) = $1$                       |

| #7 | VC    | Overflow Flag (O) = $0$                       |

| #8 | HS  | Higher or Same, Zero Flag (Z) = 1 or Carry Flag (C) = 1                                                                                                   |

|----|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| #9 | LO  | Lower, Zero Flag (Z) = 0 and Carry Flag (C) = $0$                                                                                                         |

| #A | GE  | Greater Than or Equal,<br>(Sign Flag (S) = 1 and Overflow Flag (O) = 1) or<br>(Sign Flag (S) = 0 and Overflow Flag (O) = 0)                               |

| #B | LT  | Less Than,<br>(Sign Flag (S) = 1 and Overflow Flag (O) = 0) or<br>(Sign Flag (S) = 0 and Overflow Flag (O) = 1)                                           |

| #C | GT  | Greater Than,<br>Zero Flag (Z) = 0 and<br>((Sign Flag (S) = 1 and Overflow Flag (O) = 1) or<br>(Sign Flag (S) = 0 and Overflow Flag (O) = 0))             |

| #D | LE  | Less Than or Equal,<br>Zero Flag (Z) = 1 or<br>((Sign Flag (S) = 1 and Overflow Flag (O) = 0) or<br>(Sign Flag (S) = 0 and Overflow Flag (O) = 1))        |

| #E | AL  | Always (true)                                                                                                                                             |

| #F | NEF | External Flag (E) = 0. The External Flag (E) is a flip flop that can be set by an external event, this is intended to support the IPS "pseudo interrupt". |

M CYCLES: 2

Condition Bits Affected:

None

Example:

If the Zero Flag (Z) contains 1, then after the execution of

EQ FLAG

the P0 register will contain #0001.

\* DRAFT \*

# IDX

| Operation: | P0 <<- R0      |

|------------|----------------|

|            | PSC <- PSC + 1 |

|            | PC <- PC + 2   |

### Format:

IDX

#C1

| 1 | 1 | 0 | 0 | 0 | 0 | 0 | 1 |  |

|---|---|---|---|---|---|---|---|--|

|---|---|---|---|---|---|---|---|--|

#80

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

|---|---|---|---|---|---|---|---|

|---|---|---|---|---|---|---|---|

**Description:**

The contents of the top register of the return stack (R0) are pushed onto the top of the parameter stack. The return stack remains unchanged.

M CYCLES: 2

Condition Bits Affected:

# cIN

Format:

nnnn cc cIN

The cc operand is any of the condition codes as defined for the FLAG instruction. nnnn is the address of the load value.

nnnn cc cIN

#E2

#0<cc>

LSB nnnn

MSB nnnn

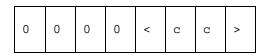

| < |  |  | n | n |  |  | > |  |

|---|--|--|---|---|--|--|---|--|

|---|--|--|---|---|--|--|---|--|

### **Description:**

If the condition cc is met then the value of the input port at the I/O address indicated by the operand nnnn is pushed onto the top of the parameter stack. Execution continues at the instruction following the operand nnnn in memory. If the condition is not met then the

address of the instruction following the operand nnnn in memory (PC + 4) is loaded into the PC register and points to the next program instruction to be executed.

M CYCLES: 3

Condition Bits Affected:

### cINB

### Format:

nnnn cc cINB

The cc operand is any of the condition codes as defined for the FLAG instruction. nnnn is the address of the load value.

nnnn cc cINB

#E4

#0<cc>

LSB nnnn

MSB nnnn

| < |  |  | n | n |  |  | > |  |

|---|--|--|---|---|--|--|---|--|

|---|--|--|---|---|--|--|---|--|

### **Description:**

If the condition cc is met then the value of the input port at the I/O address indicated by the operand nnnn is pushed into the least significant byte of the P0 register. The most significant byte of P0 is filled with zeroes. Execution continues at the instruction following

the operand nnnn in memory. If the condition is not met then the address of the instruction following the operand nnnn in memory (PC + 4) is loaded into the PC register and points to the next program instruction to be executed.

M CYCLES: 3

Condition Bits Affected:

### cpIN

<u>Operation:</u> if condition cc = 0

Format:

cc cpIN

The cc operand is any of the condition codes as defined for the FLAG instruction

cc cpIN

#EA

#0<cc>

| 0 | 0 | 0 | 0 | < | С | С | > |  |

|---|---|---|---|---|---|---|---|--|

|---|---|---|---|---|---|---|---|--|

### Description:

If the condition cc is met then the value of the input port at the I/O address indicated by the contents of the top register of the parameter stack (P0) is loaded into the P0 register. If the condition is not met, then the top entry of the parameter stack is popped and discarded.

M CYCLES: 3 if condition cc is met; 2 otherwise.

### Condition Bits Affected:

### cpINB

Operation: if condition cc = 0

Z <- 0 PSC <- PSC - 1 PC <- PC + 2

Format:

cc cpINB

The cc operand is any of the condition codes as defined for the FLAG instruction

cc cpINB

#EC

| 1 | 1 | 1 | 0 | 1 | 1 | 0 | 0 |

|---|---|---|---|---|---|---|---|

|---|---|---|---|---|---|---|---|

#0<cc>

| 0 | 0 | 0 | 0 | < | С | С | > |  |

|---|---|---|---|---|---|---|---|--|

|---|---|---|---|---|---|---|---|--|

### Description:

If the condition cc is met then the value of the input port at the I/O address indicated by the contents of the top register of the parameter stack (P0) is loaded into the least significant byte of the P0 register. The most significant byte of P0 is filled with zeroes. If the condition is not met, then the top entry of the parameter stack is popped and discarded.

M CYCLES: 3 if condition cc is met; 2 otherwise.

### Condition Bits Affected:

### cJMP

<u>Operation:</u> if condition cc = 0

PC <- PC + 4

if condition cc = 1 PC <- nnnn

### Format:

nnnn cc cJMP

The cc operand is any of the condition codes as defined for the FLAG instruction. nnnn is the destination address.

nnnn cc cJMP

#81

| 1 0 0 0 0 0 0 | 1 |

|---------------|---|

|---------------|---|

#0<cc>

| 0 | 0 | 0 | 0 | < | С | С | > |

|---|---|---|---|---|---|---|---|

|---|---|---|---|---|---|---|---|

LSB nnnn

| < |  | n | n |  |  | > |

|---|--|---|---|--|--|---|

|---|--|---|---|--|--|---|

MSB nnnn

### Description:

If the condition cc is met then the destination address nnnn is loaded into the Program Counter Register (PC) and points to the address of the next program instruction to be executed. If the condition is not met then the address of the instruction following the destination address in memory (PC + 4) is loaded into the PC register and points to the next program instruction to be executed.

The assembler provides the following definitions to aid the computation of jump addresses:

cc cJMPbeginStores opcode and leaves address of the place to insert the jump<br/>address on top of the IPS-X parameter stack.cJMPelseCalculates and inserts the required jump address into the address<br/>previously deposited by cJMPbegin on the top of the IPS-X<br/>parameter stack. The address is popped and discarded. Then an<br/>AL cJMP is assembled into the code, and the address of the place<br/>to insert the jump address is pushed onto the top of the IPS-X<br/>parameter stack.cJMPendCalculates and inserts the required jump address into the address<br/>previously deposited by cJMPbegin or cJMPelse. The address is<br/>popped and discarded.

M CYCLES: 3

Condition Bits Affected:

### срЈМР

<u>Operation:</u> if condition cc = 0

Format:

cc cpJMP

The cc operand is any of the condition codes as defined for the FLAG instruction.

cc cpJMP

#89

| 1 0 | 0 0 | 1 | 0 | 0 | 1 |  |

|-----|-----|---|---|---|---|--|

|-----|-----|---|---|---|---|--|

#0<cc>

| 0 | 0 | 0 | 0 | < | С | С | > |

|---|---|---|---|---|---|---|---|

|---|---|---|---|---|---|---|---|

### Description:

If the condition cc is met then the top of the parameter stack is popped into the Program Counter Register (PC) and points to the address of the next program instruction to be executed. If the condition is not met then the top entry of the parameter stack is popped and the address of the next instruction in memory (PC + 2) is loaded into the PC register and points to the next program instruction to be executed.

### M CYCLES: 2

Condition Bits Affected:

### sJMP

Operation: PC <- abc

Format:

abc sJMP

#0<a>

| 0 0 | 0 | 0 | < | a |  | > |  |

|-----|---|---|---|---|--|---|--|

|-----|---|---|---|---|--|---|--|

<b><c>

| < | b |  | > | < | С |  | > |  |

|---|---|--|---|---|---|--|---|--|

|---|---|--|---|---|---|--|---|--|

#### Description:

Unconditional jump to a 12-bit address specified by abc. The operand abc is loaded into the Program Counter Register (PC) and points to the address of the next program instruction to be executed.

The assembler provides the following definitions to aid the computation of jump addresses:

- sJMPbegin Stores opcode and leaves address of the place to insert the jump address on top of the IPS-X parameter stack.

- sJMPcomplete Calculates and inserts the required jump address into the address previously deposited by sJMPbegin. The address is popped and discarded.

M CYCLES: 2

**Condition Bits Affected:**

### JPPC

Operation: PPC <<- (PPC) PC <- PC + 2

Format:

JPPC

#FC

| 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 |  |

|---|---|---|---|---|---|---|---|--|

|---|---|---|---|---|---|---|---|--|

#00

| 0 0 0 0 0 0 0 0 |

|-----------------|

|-----------------|

### Description:

The contents of the word in memory at the address indicated by the contents of the Pseudo Program Counter Register (PPC) are loaded into the PPC register. Program execution continues at the next instruction in memory (PC + 2).

M CYCLES: 3

Condition Bits Affected:

## cJSR

<u>Operation:</u> if condition CC = 0PC <- PC + 4

```

if condition cc = 1

R0 <- PC + 4

RSC <- RSC + 1

PC <- nnn

```

### Format:

nnnn cc cJSR

The cc operand is any of the condition codes as defined for the FLAG instruction. nnnn is the address of a subroutine.

#### nnnn cc cJSR

#80

| #00 |   |   |   |   |   |   |   |

|-----|---|---|---|---|---|---|---|

| 1   | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

#0<cc>

| 0 | 0 | 0 | 0 | < | С | С | > |  |

|---|---|---|---|---|---|---|---|--|

|---|---|---|---|---|---|---|---|--|

LSB nnnn

| < |  | n | n |  |  | > |

|---|--|---|---|--|--|---|

|---|--|---|---|--|--|---|

MSB nnnn

### Description:

If the condition cc is met then the address of the instruction following the subroutine address in memory (PC + 4) is pushed onto the top of the return stack. The subroutine address nnnn is loaded into the Program Counter Register (PC) and points to the address of the next program instruction to be executed. If the condition is not met then the address of the instruction following the subroutine address in memory (PC + 4) is loaded into the PC register and points to the next program instruction to be executed.

The assembler provides the following definitions to aid the computation of jump addresses:

| cc cJSRbegin | Stores opcode and leaves address of the place to insert the jump address on top of the IPS-X parameter stack.                             |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| cJSRcomplete | Calculates and inserts the required jump address into the address previously deposited by cJSRbegin. The address is popped and discarded. |

M CYCLES: 3

Condition Bits Affected:

# cpJSR

| Operation: | if condition cc = 0<br>PSC <- PSC - 1<br>PC <- PC + 2                                |

|------------|--------------------------------------------------------------------------------------|

|            | if condition cc = 1<br>R0 <<- PC + 2<br>RSC <- RSC + 1<br>PC <- P0<br>PSC <- PSC - 1 |

Format:

cc cpJSR

The cc operand is any of the condition codes as defined for the FLAG instruction.

cc cpJSR

#88

#0<cc>

| 0 | 0 | 0 | 0 | < | С | С | > |  |

|---|---|---|---|---|---|---|---|--|

|---|---|---|---|---|---|---|---|--|

#### Description:

If the condition cc is met then the address of the next instruction in memory (PC + 2) is pushed onto the return stack. Top of the parameter stack is popped into the Program Counter Register (PC) and points to the address of the next program instruction to be executed. If the condition is not met then the top of the parameter stack is popped and the address of the next instruction in memory (PC + 2) is loaded into the PC register and points to the next program instruction to be executed.

#### M CYCLES: 3

Condition Bits Affected:

### sJSR

| Operation: | R0 <<- PC + 2  |

|------------|----------------|

|            | RSC <- RSC + 1 |

|            | PC <- abc      |

Format:

abc sJSR

#1<a>

| 0 | 0 | 0 | 1 | < | a | > |

|---|---|---|---|---|---|---|

|   |   |   |   |   |   |   |

<b><c>

| < b | > | < | С |  | > |  |

|-----|---|---|---|--|---|--|

|-----|---|---|---|--|---|--|

Description:

Unconditional jump to a subroutine whose 12-bit address is specified by abc. The address of the next instruction in memory (PC + 2) is pushed onto the return stack, then the operand abc is loaded into the Program Counter Register (PC) and points to the address of the next program instruction to be executed.

The assembler provides the following definitions to aid the computation of jump addresses:

- sJSRbegin Stores opcode and leaves address of the place to insert the jump address on top of the IPS-X parameter stack.

- sJSRcomplete Calculates and inserts the required jump address into the address previously deposited by sJSRbegin. The address is popped and discarded.

M CYCLES: 3

Condition Bits Affected:

## cLOAD

Format:

nnnn cc cLOAD

The cc operand is any of the condition codes as defined for the FLAG instruction. nnnn is the address of the load value.

nnnn cc cLOAD

#82

#0<cc>

LSB nnnn

MSB nnnn

| < |  |  | n | n |  |  | > |  |

|---|--|--|---|---|--|--|---|--|

|---|--|--|---|---|--|--|---|--|

#### **Description:**

If the condition cc is met then the word located at memory address indicated by the operand nnnn is pushed onto the top of the parameter stack. Execution continues at the instruction following the operand nnnn in memory. If the condition is not met then the

address of the instruction following the operand nnnn in memory (PC + 4) is loaded into the PC register and points to the next program instruction to be executed.

M CYCLES: 3

Condition Bits Affected:

## cLOADB

Format:

nnnn cc cLOADB

The cc operand is any of the condition codes as defined for the FLAG instruction. nnnn is the address of the load value.

nnnn cc cLOADB

#84

#0<cc>

LSB nnnn

MSB nnnn

| < |  |  | n | n |  |  | > |  |

|---|--|--|---|---|--|--|---|--|

|---|--|--|---|---|--|--|---|--|

#### Description:

If the condition cc is met then the byte located at memory address indicated by the operand nnnn is pushed onto the top of the parameter stack. The byte is placed into the least significant byte of the P0 register; the upper byte being filled with zeroes.